Int. J. Electron. Commun. (AEÜ) 61 (2007) 300-306

www.elsevier.de/aeue

# On the realization of electronically current-tunable CMOS OTA

# Khanittha Kaewdang\*, Wanlop Surakampontorn

Faculty of Engineering and Research Center for Communication and Information Technology (ReCCIT), King Mongkut's Institute of Technology Ladkrabang (KMITL), Ladkrabang, Bangkok 10520, Thailand

Received 2 September 2005

#### **Abstract**

A CMOS operational transconductance amplifier (OTA) called as an EOTA, where its transconductance gain can be electronically and linearly tuned is proposed in this paper. The realization method is achieved by squaring the transconductance gain of the balanced CMOS OTA. The EOTA transconductance gain can be linearly tuned by an external bias current for three decades. The linear input-voltage range of about 1 Vp with less than 1% nonlinearity is obtained. The usefulness of the proposed EOTA is demonstrated through application example with a current multiplier. The performance of the proposed circuit is discussed and confirmed through PSPICE-simulation results.

© 2006 Elsevier GmbH. All rights reserved.

Keywords: CMOS OTA; Electronically and linearly tuned; Current controlled

# 1. Introduction

Linear transconductors or voltage-to-current converter circuits are fundamental building blocks of analog circuits and systems. They are found useful in interface circuits, instrumentation amplifiers, continuous-time-filters and oscillators. In addition, when the transconductance gain of the transconductor can be electronically varied, they can also be applied in automatic gain control circuits and in analog multipliers. In the last two decades, it is well accepted that a linear transconductor, which is constructed from a bi-polar differential pair and current mirrors, called as an operational transconductance amplifier (OTA), is one of the essential active building blocks in the design of analog circuits [1-3]. This is due to the fact that the OTA is a low-cost device that has only a single high-impedance node and its transconductance gain  $g_m$  can be linearly controlled over more than four decades by means of an external bias current. Moreover, the implementation of analog circuits in such a way that employs only OTA as standard cells will not only be easily constructed from readily commercial available IC, but also significantly simplified the design.

In CMOS technology, several linearly tunable transconductors based on the use of MOS transistors operating in saturation region have been proposed in the literature [4–7]. Most of them are functioning in voltage-controlled mode. The method of source-follower of Ref. [4] is operated in square law characteristic with constant source-bulk voltages, where the control voltage is applied to the gate. Whereas for the cross-coupled connection methods [5-7], the transconductance control voltages are applied through voltage-level shifters. However, their controllable voltage ranges are rather limited and only narrow linearly tunable transconductance ranges are available. In some applications, such as, an analog multiplier circuit, a frequency divider/multiplier circuit and an arbitrary power-law circuit, current-controlled transconductors that this transconductance gain can be linearly controllable by a DC bias current are preferable [8–10]. In the past, a current-controlled CMOS transconductor was

<sup>\*</sup> Corresponding author. E-mail address: s5160306@kmitl.ac.th (K. Kaewdang).

presented in Ref. [11]. But the linearly tunable transconductance range is narrow due to the MOS transistors are working in the weak-inversion region.

The main objective of this paper is, therefore, to present a circuit design technique for the synthesis of a linear electronically tunable CMOS OTA, called as an EOTA. Since, the realization method is achieved by squaring the transconductance gain of the CMOS OTA, the transconductance gain of the EOTA is directly depend on the DC bias current. To provide a maximum output voltage swing and wide linearly tunable transconductance range, a balanced CMOS OTA or voltage-to-current transducer will be employed as basic active circuit elements to realize the EOTA, whereas the completed EOTA requires three balanced CMOS OTA's. Since it is generally assumed that all MOS transistors are operating in the saturation region, the individual functions of the circuits are derived from the approximate square-law characteristic of MOS transistors in saturation. In addition, it is well accepted that the design and implementation of electronically tunable analog circuits using bipolar-based OTA as active circuit elements are well established and well tabulated. Then, having access to such a linear electronically tunable CMOS OTA, it would enable us to realize CMOS analog circuits with their property can be electronically tuned by simply replacing a bipolar OTA with an EOTA. This kind of advantage will be demonstrated through an application example. The proposed EOTA is employed to implement a current multiplier circuit, that using only active elements and without the requirement of external passive elements. The circuit performances are studied through PSPICE-simulation results.

#### 2. Circuit description

For the purpose of the following analysis, we will assume that all MOS devices operate in the saturation region. This means that the transistor drain current  $I_D$  is characterized by a square-law model as

$$I_{D} = K(V_{GS} - V_{T})^{2} \quad \text{for } V_{GS} > V_{T},$$

$$= 0 \quad \text{for } V_{GS} \leqslant V_{T}, \tag{1}$$

where the transconductance parameter  $K = \mu C_{\rm ox} W/2L$ ,  $\mu$  is the mobility of the carrier,  $C_{\rm ox}$  is the gate-oxide capacitance per unit area, W is the effective channel width, L is the effective channel length, and  $V_{\rm GS}$  and  $V_{\rm T}$  are the gate-to-source and the threshold voltages, respectively.

#### 2.1. A balanced CMOS OTA

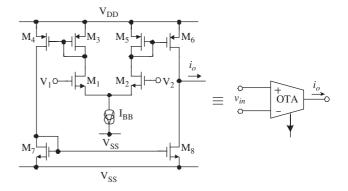

Fig. 1 shows a balanced single-output CMOS OTA, which is formed by MOS coupled pair and current mirrors, where  $V_{\rm in}$  is the differential input voltage  $(V_{\rm in} = V_1 - V_2)$ ,  $i_{\rm o}$  is the output current and  $I_{\rm BB}$  is the bias current. Let us assume that  $M_1$  and  $M_2$  are perfectly matched and the current mirrors

Fig. 1. Schematic diagram of a balanced CMOS OTA.

have unity current gain. By using Eq. (1), the differential output current of the circuit in Fig. 1 can be given by [12]

$$i_{o} = i_{2} - i_{1}$$

$$= \sqrt{2I_{BB}K}V_{in}\sqrt{1 - \frac{KV_{in}^{2}}{2I_{BB}}} \quad \text{for}$$

$$-\sqrt{\frac{I_{BB}}{K}} \leqslant V_{in} \leqslant \sqrt{\frac{I_{BB}}{K}}.$$

(2)

The transconductance gain  $(g_m)$  of the fully differential OTA can be derived by taking the derivative of Eq. (2) with respect to  $V_{\text{in}}$ , yielding

$$g_{m} = \frac{\mathrm{d}i_{o}}{\mathrm{d}V_{\mathrm{in}}} \Big|_{V_{\mathrm{in}}=0}$$

$$= \sqrt{2I_{\mathrm{BB}}K} \quad \text{for}$$

$$-\sqrt{\frac{I_{\mathrm{BB}}}{K}} \leqslant V_{\mathrm{in}} \leqslant \sqrt{\frac{I_{\mathrm{BB}}}{K}}.$$

(3)

From Eq. (2), the current  $i_0$  can written as

$$i_{\rm o} = g_m V_{\rm in} = \sqrt{2I_{\rm BB}K} V_{\rm in}. \tag{4}$$

Eq. (3) shows that the transconductance gain  $(g_m)$  of the OTA can be varied by the bias current  $I_{\rm BB}$ , but in the form of square root function. In addition, in order to operate in the low distortion range, where all the transistors are operated in saturation, the input voltage  $V_{\rm in}$  should be in the range of [13]

$$V_{\rm in} \leqslant \left| \sqrt{I_{\rm BB}/K} \right|$$

(5)

# 2.2. The proposed electronically and linearly tunable CMOS OTA

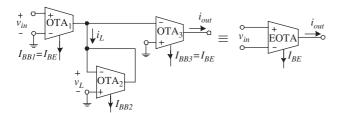

Through the use of three balanced single-output CMOS OTAs, a CMOS-based electronically and linearly tunable OTA, called as an EOTA, can be realized by the circuit diagram shown in Fig. 2. The OTA<sub>1</sub> converts a differential input signal voltage  $v_{\rm in} = v_1 - v_2$  into a signal current  $i_{\rm L}$  to

Fig. 2. The proposed EOTA.

flow into an active resistor  $R_L$ , formed by the OTA<sub>2</sub>, where  $Z_L = 1/g_{m2}$  and  $g_{m2}$  represents the transconductance gain of the OTA<sub>2</sub>. Since the current signal  $i_L = g_{m1}v_{in}$ , the voltage drop across the active resistor (OTA<sub>2</sub>) becomes

$$v_{\rm L} = i_{\rm L} z_{\rm L} = g_{m1} v_{\rm in} \frac{1}{g_{m2}}.$$

(6)

The OTA<sub>3</sub> will convert the voltage  $v_L$ , with the transconductance gain of  $g_{m3}$ , into the output current  $i_{out}$  as

$$i_{\text{out}} = g_{m3}v_{\text{L}} = g_{m1}v_{\text{in}}\frac{1}{g_{m2}}.$$

(7)

From Eqs. (6) and (7), the current  $i_{out}$  can be rewritten as

$$i_{\text{out}} = \frac{g_{m1}g_{m3}}{g_{m2}} v_{\text{in}}.$$

(8)

Since  $g_{m1} = \sqrt{2I_{\text{BB}1}K_1}$ ,  $g_{m2} = \sqrt{2I_{\text{BB}2}K_2}$  and  $g_{m3} = \sqrt{2I_{\text{BB}3}K_3}$ , if we set  $I_{\text{BB}1} = I_{\text{BB}3} = I_{\text{BE}}$ , then from Eq. (8), we obtain

$$i_{\text{out}} = \frac{2I_{\text{BE}}\sqrt{K_1K_3}}{\sqrt{2I_{\text{BB}2}K_2}} v_{\text{in}} = g_{mT}v_{\text{in}},$$

(9)

where  $g_{mT}$  represents the transconductance gain of the proposed EOTA and can be expressed as

$$g_{mT} = 2I_{BE}K_{T} \tag{10}$$

and  $K_{\rm T} = \sqrt{K_1 K_3/2 I_{\rm BB2} K_2}$ , which can usually be kept at constant. Eq. (10) clearly indicted that the transconductance gain of the proposed EOTA can be electronically and linearly tuned by the bias current  $I_{\rm BE}$ . This linear relationship is in the form that similar to the transconductance gain of the bi-polar-based OTA that found useful in many applications [14]. Since the balanced CMOS OTA is formed by MOS coupled pair and current mirrors, therefore, the proposed EOTA is very suitable for fabricating in CMOS integrated form.

#### 3. Performance of the EOTA

It is well accepted that the prediction of Eq. (10) will be valid only for a small value of  $V_{\rm in}$ . From Eq. (5), since OTA<sub>1</sub> and OTA<sub>3</sub> are formed by MOS coupled pairs, to maintain in the linear range and low total harmonic distortion, the voltages  $V_{\rm in}$  and  $V_{\rm L}$  should, respectively, be restricted to the

ranges of [13]

$$|V_{\rm L}|_{\rm MAX} = 0.4/\sqrt{2}K Z_{\rm L}$$

and

$$|V_{\rm in}|_{\rm MAX} = 0.4\sqrt{I_{\rm BB}/K},$$

(11)

where it should be noted from Eq. (11) that the maximum usable voltage range is limited by  $|V_L|_{\rm MAX}$  if  $g_{m1}/g_{m2} > 1$  and it is limited by  $|V_{\rm in}|_{\rm MAX}$  if  $g_{m1}/g_{m2} < 1$ . For example, for  $I_{\rm BE} = 1$  mA and  $I_{\rm BB2} = 700$   $\mu$ A, the maximum usable range is determined by  $|V_L|_{\rm MAX}$  and  $|V_L|_{\rm MAX}$  is about 0.94 V, for  $K = \mu_n C_{\rm ox} W/2L = 1.27 \times 10^{-4} {\rm A/V}^2$ ,  $\mu_n C_{\rm ox} = 5.08 \times 10^{-5} {\rm V}$  and W/2L = 2.5.

The transconductance gain error that results from in the inaccuracy of the EOTA can be determined from a large signal analysis. Consider the balanced CMOS OTA, the transconductance gain  $G_m$  of the Eq. (2) can be written as

$$G_{m} = \frac{i_{\text{out}}}{V_{\text{in}}}$$

$$= \sqrt{2I_{\text{BB}}K} \sqrt{1 - \frac{KV_{\text{in}}^{2}}{2I_{\text{BB}}}} \quad \text{for}$$

$$-\sqrt{\frac{I_{\text{BB}}}{K}} \leqslant V_{\text{in}} \leqslant \sqrt{\frac{I_{\text{BB}}}{K}}. \tag{12}$$

If we set the transconductance error of the balanced CMOS OTA of Fig. 1 as  $E = KV_{in}^2/2I_{BB}$ , then Eq. (12) can be rewritten as

$$G_m = \frac{i_{\text{out}}}{V_{\text{in}}} = \sqrt{2I_{\text{BB}}K}\sqrt{1 - E}.$$

(13)

We found that the  $G_m$  will equal to the  $g_m$  of Eq. (3) in the condition that  $KV_{\rm in}^2/2I_{\rm BB} \ll 1$ . This can be achieved by keeping the input voltage signal  $V_{\rm in}$  small or set the DC bias current  $I_{\rm BB}$  to a large value.

By applying the  $G_m$  of Eq. (13) to the circuit of Fig. 2, we obtain the transconductance gain of the proposed EOTA for large signal as

$$G_{mT} = 2I_{BB}K_{T}\left(1 + \frac{\sqrt{1 - E_{1}}\sqrt{1 - E_{3}} - \sqrt{1 - E_{2}}}{\sqrt{1 - E_{2}}}\right),$$

(14)

where the errors  $E_1 = K_1 V_{\rm in1}^2 / 2I_{\rm BB1}$ ,  $E_2 = K_2 V_{\rm in2}^2 / 2I_{\rm BB2}$  and  $E_3 = K_3 V_{\rm in3}^2 / 2I_{\rm BB3}$  are the transconductance errors due to the OTA<sub>1</sub>, OTA<sub>2</sub> and OTA<sub>3</sub>, respectively. Given that  $E_{\rm T}$  is the transconductance error of the EOTA from the linear transconductance gain, we can write

$$E_{\rm T} = \frac{\sqrt{1 - E_1}\sqrt{1 - E_3} - \sqrt{1 - E_2}}{\sqrt{1 - E_2}}.$$

(15)

Thus, we have the percent of the conversion error as

%

$$E_{\rm T} = \frac{\sqrt{1 - E_1}\sqrt{1 - E_3} - \sqrt{1 - E_2}}{\sqrt{1 - E_2}} \times 100\%.$$

(16)

For example, if  $V_{\text{in}1} = 0.5 \text{ V}$ ,  $V_{\text{in}2} = V_{\text{in}3} = 0.751 \text{ V}$ ,  $I_{\text{BB}1} = I_{\text{BB}3} = I_{\text{BE}} = 1 \text{ mA}$ ,  $I_{\text{BB}2} = 700 \,\mu\text{A}$  and  $K_1 = K_2 = K_3 = 1.27 \times 10^{-4} \,\text{A/V}^2$ , the resulting transconductance error (%  $E_{\text{T}}$ ) is equal to 0.54%.

### 4. A current multiplier circuit

In order to demonstrate the applications and the usefulness of the proposed EOTA, an application example will be outlined in this section. It outlines the use of the EOTA to realize the current-mode multiplier which employs only active circuit elements.

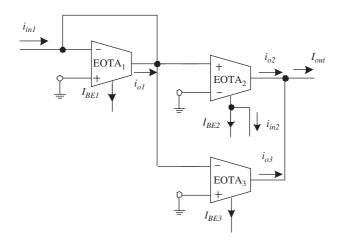

The current multiplier circuit is shown in Fig. 3. This application is adapted from the bipolar-based OTA-based circuits by replacing the bipolar-based OTA with the proposed EOTA [15]. From the figure, the input signal current  $i_{\text{in}1}$  is injected into the EOTA<sub>1</sub>, which is connected as a current-controlled grounded resistor. The voltage across the EOTA<sub>1</sub> is then used as the input voltage for the EOTA<sub>2</sub> and EOTA<sub>3</sub>. The input signal current  $i_{\text{in}2}$  is added with the bias current  $I_{\text{B2}}$  of the EOTA<sub>2</sub>. Let  $g_{m\text{T1}}$ ,  $g_{m\text{T2}}$  and  $g_{m\text{T3}}$  be the transconductance gains of the EOTA<sub>1</sub>, EOTA<sub>2</sub> and EOTA<sub>3</sub>, respectively. Then from Eq. (9) and from routine circuit analysis the output currents  $i_{\text{o}2}$  and  $i_{\text{o}3}$  of the EOTA<sub>2</sub> and EOTA<sub>3</sub>, respectively, can be written as

$$i_{o2} = \frac{g_{mT1}}{g_{mT1}} i_{\text{in}1} = \frac{(I_{\text{BE2}} + i_{\text{in}2})}{I_{\text{BE1}}} i_{\text{in}1}$$

(17)

and

$$i_{03} = -\frac{g_{mT3}}{g_{mT1}}i_{\text{in1}} = -\frac{I_{\text{BE3}}}{I_{\text{BE1}}}i_{\text{in1}},$$

(18)

where  $I_{\text{BE1}}$ ,  $I_{\text{BE2}}$  and  $I_{\text{BE3}}$  represent the DC bias current of the EOTA<sub>1</sub>, EOTA<sub>2</sub> and EOTA<sub>3</sub>, respectively, and the transconductance gains  $g_{m\text{T1}} = 2I_{\text{BE1}}K_{\text{T1}}$ ,  $g_{m\text{T2}} = 2(I_{\text{BE2}} + i_{\text{in2}})K_{\text{T2}}$  and  $g_{m\text{T3}} = 2I_{\text{BE3}}K_{\text{T3}}$ . If we set  $I_{\text{BE2}} = I_{\text{BE3}} = I_{\text{B}}$ ,

Fig. 3. The multiplier circuit using EOTA.

the output current  $I_{\text{out}}$  of the circuit that is the summation of the currents  $i_{02}$  and  $i_{03}$  can be expressed as

$$I_{\text{out}} = i_{02} + i_{03} = \frac{i_{\text{in}1}i_{\text{in}2}}{I_{\text{BE1}}},$$

(19)

which is in the form of a current multiplication function.

#### 5. Simulation results

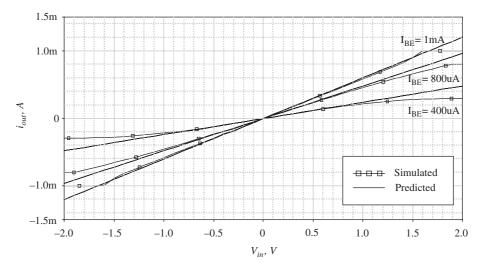

The performance of the proposed EOTA of Fig. 2 and its applications were verified through the use of PSPICEsimulation results. All the balanced CMOS OTA was simulated by using CMOS transistor parameters of the SCN2 level 2 of MOSIS [16]. The dimensions of transistors  $M_1$ and  $M_2$  are  $W = 50 \,\mu\text{m}$  and  $L = 10 \,\mu\text{m}$ , the dimensions of the transistor  $M_3 - M_8$  are  $W = 100 \,\mu\text{m}$  and  $L = 10 \,\mu\text{m}$ . The power supply voltage were set to  $V_{\rm DD} = -V_{\rm SS} = \pm 5 \, \rm V$ . Fig. 4 shows the simulated transfer characteristic of the EOTA of Fig. 2. The plots of the output current  $I_{out}$  versus the input voltage  $V_{\rm in}$  show that, for the DC bias current ( $I_{\rm BE}$ ) in the cases of 1 mA,  $800\,\mu\text{A}$  and  $400\,\mu\text{A}$ , the EOTA can linearly convert the input voltage into output signal current with nonlinearity of less than 1% for the input voltage  $(V_{in})$  in the ranges of -1 to 1V, -0.86 to 0.86 V and -0.66 to 0.66 V, respectively. These results were agreed with the prediction value from Eq. (9). For example, for the case of the DC bias current  $I_{BE} = 1 \text{ mA}$  and for  $V_{in} = 0.86 \text{ V}$ ,  $I_{BB2} = 700 \,\mu\text{A}$ , the transconductance gain  $g_{mT} = 5.398 \times 10^{-4} \text{ A/V}$ , where the conversion error is about 0.5%. The frequency response of the EOTA was also studied, where the  $-3 \, dB$  bandwidth of about 120 MHz is achieved.

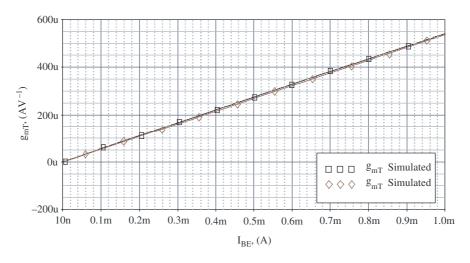

The plot of the relation between the transconductance gain  $g_{m\rm T}$  and the bias current  $I_{\rm BE}$  in Fig. 5 is measured by fixing  $V_{\rm in}=0.1\,\rm V$  and varying  $I_{\rm BE}$  from 10 nA to 1 mA. It shows that the transconductance gain  $g_{m\rm T}$  can be linearly tuned by the bias current  $I_{\rm BE}$  over the range of 1  $\mu$ A–1 mA (three decades), where the simulated conversion error found to be about 0.68%. The similar relation of  $g_{m\rm T}$  versus  $I_{\rm BE}$  are also obtained for the cases of fixing  $V_{\rm in}=0.2\,\rm V$  and  $V_{\rm in}=0.5\,\rm V$ . But in these cases the linear tunable ranges should be started at the current  $I_{\rm BE}$  that must more than 5 and 32  $\mu$ A, respectively, since the entire MOS transistors must be operated in saturation region.

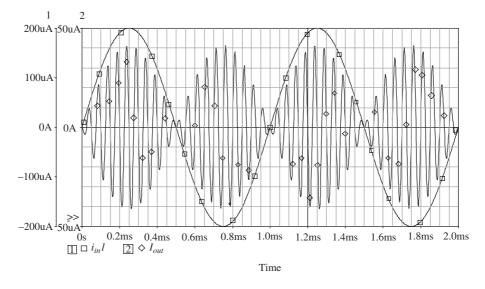

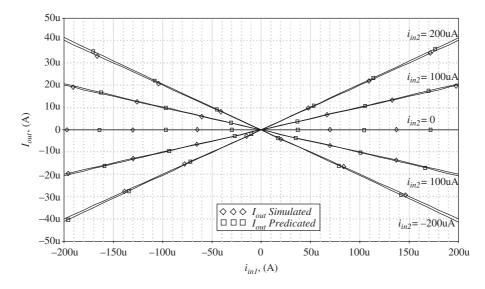

To demonstrate that the circuit of Fig. 3 can be functioned as current multiplier, two sinusoidal current signals are applied. Fig. 6 shows the response for the case of  $i_{\rm in1}=0.2\sin(2\pi1000t)\,{\rm mA},\ i_{\rm in2}=0.2\sin(2\pi20\,000t)\,{\rm mA}$  and  $I_{\rm B1}=1\,{\rm mA}.$  This result confirms that the circuit can accurately modulate two different input signal currents. The DC transfer characteristics of the multiplier circuit shown in Fig. 7 were observed by setting the bias currents  $I_{\rm B1}=I_{\rm B2}=I_{\rm B3}=1\,{\rm mA},$  and the input current  $i_{\rm in1}$  and  $i_{\rm in2}$  are varied from  $-200\,{\rm \mu A}$  to  $200\,{\rm \mu A}$  with  $100\,{\rm \mu A}$  per step. The transfer characteristic demonstrated that the simulated and calculated data are agreed very well over the input range of

Fig. 4. DC transfer characteristics of the EOTA.

Fig. 5. Linear transconductance tunable range.

Fig. 6. Simulated transient response of the multiplier circuit.

Fig. 7. Simulated DC transfer characteristic of the multiplier.

190 μA with the error of less than 1%. The high-frequency characteristic of the multiplier circuit is also studied. The simulated -3 dB bandwidth for the case of the input  $i_{\text{in}1}$  to the output  $I_{\text{out}}$ , with  $i_{\text{in}1} = 0.5 \sin(2\pi 10\,000t)$  mA,  $i_{\text{in}2} = 500$  μA and  $I_{\text{B}1} = 1$  mA, is about 75 MHz and the simulated -3 dB bandwidth of the circuit for the input  $i_{\text{in}2}$  to the output  $I_{\text{out}}$ , with  $i_{\text{in}2} = 0.5 \sin(2\pi 10\,000t)$  mA,  $i_{\text{in}1} = 500$  μA and  $I_{\text{B}1} = 1$  mA, is about 71 MHz.

#### 6. Conclusion

A design of the CMOS-based electronically and linearly current-tunable OTA has been proposed. The EOTA circuit composed of three balanced CMOS OTAs which is suitable for implementing in CMOS integrated form. The achieve characteristics of the proposed circuit were similar as the bipolar OTA that the transconductance gain  $(g_m)$  can be linearly tuned by the DC bias current. Simulation results have been employed to demonstrate the performances of the proposed EOTA. Moreover to confirm that EOTA can be replacing the bipolar OTA, the current-mode multiplier circuit is used to display the performances of the proposed circuit.

### Acknowledgments

This work was funded by the Thailand Research Fund through the Royal Golden Jubilee Ph.D. Program (Grant No. PHD/0107/2546) to Khanittha Kaewdang and Wanlop Surakampontorn and financial support from the Thailand Research Fund (TRF) under the Senior Research Scholar Program, Grant No. RTA4680003 acknowledge these supports.

## References

- [1] Senani R. A simple approach of deriving single-input-multiple-output current-mode biquad filters. Electron Lett 1989;25:19–21.

- [2] Chung WS, Kim KH, Cha HW. A linear operational transconductance amplifier for instrumentation applications. IEEE Trans Instrum Meas 1992;41:441–3.

- [3] Iqbal Khan A, Ahmed Muslim T. Wide-range electronically tunable multifunctional OTA-C filter for instrumentation applications. IEEE Trans Instrum Meas 1987;IM-36:13-7.

- [4] Klumperink E, Zwan EVD. CMOS variable transconductance circuit with constant bandwidth. Electron Lett 1989;25: 675–6.

- [5] Huang S-C, Ismail M. Linear tunable COMFET transconductor. Electron Lett 1993;29:459–61.

- [6] Wang Z, Guggenbuhl W. A voltage-controllable linear MOS transconductor using bias offset technique. IEEE Solid State Circuits 1990;25:315–7.

- [7] Wilson G, Chan PK. Saturation-mode CMOS transconductor with enhanced tunability and low distortion. Electron Lett 1993;29:459–61.

- [8] Silva-Martinez J, Sanchez-Sinencio E. Analogue OTA multiplier without input voltage swing restrictions and temperature-compensated. Electron Lett 1986;22:599–600.

- [9] Tarun SK, Arabinda R, Baidyanath RN. An arbitrary powerlaw device based on operational transconductance amplifiers. IEEE Trans Instrum Meas 1993;42:948–52.

- [10] Abuelma'atti MT. A novel analogue current-mode current-controlled frequency divider/multiplier. Int J Electron 2002;89:455–65.

- [11] Hung C-C, Halonen K. Micropower CMOS GM-C filters for speech signal processing. In: IEEE International Symposium on Circuit and Systems. 1997. p. 1972–4.

- [12] Surakampontorn W, Kumwachara K, Riewruja V, Surawatpunya C. CMOS-based integrable electronically tunable floating general impedance inverter. Int Electron 1997;82: 33–44.

- [13] Toumazu C, Lidgey FT, Haigh DG. The current mode approach. London, UK: Peter Feregrinus; 1990.

- [14] National Semiconductor. Dual operational transconductance amplifiers with linearizing diodes and buffers. General purpose linear devices databook, 1989.

- [15] Kaewdang K, Fongsamut C, Surakampontorn W. A realization of biquadratic circuit using MO-CCIIs and capacitors. In: IEEE international symposium on circuit and systems Bangkok. Thailand, 2003. p. 349–54.

- [16] Elwan HO, Soliman AM. Low-voltage low-power CMOS current conveyors. IEEE Trans Circuits Systems 1997;44: 828–35.

Khanittha Kaewdang was born in Sisaket, Thailand. She received her B. Eng. degree in Electrical Engineering from the Ubon Rajathanee University, Ubon Rajathanee, Thailand, in 1999 and M. Eng. degree in Electronics Engineering from the King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 2002. She is currently working toward the

Dr. Eng. degree at the KMITL. Her research interests include analog signal-processing, analog integrated circuit, and electronic instrumentation.

Wanlop Surakampontorn (S'80–M'84) was born in Bangkok, Thailand. He received his B. Eng. and M. Eng. degrees in Electrical Engineering from the King Mongkut's Institute of Technology Lad-krabang (KMILT), Bangkok, Thailand, in 1976, and 1978, respectively, and his Ph.D. in Electronics from the University of Kent at Canterbury, Kent, UK, in 1983. Since 1978, he has been a Member of the Department of Electronics,

Faculty of Engineering, KMITL, where he is currently a Professor of Electronic Engineering. His research interests are in the areas of analog and digital integrated circuit designs, real-time application of PC computers and microprocessors, digital signal processing, electronic instrumentation, and VLSI signal processing.

Dr. Surakampontorn received the Outstanding Scientist of Thailand Award in 1996 and The National Award for Distinguished Researcher, Thailand, in 1998. He is a Senior Member of the IEEE and is a Member of the IEICE.